Using a Supervisory Circuit to Turn a Conventional SRAM into Fast Non-Volatile Memory - Technical Articles

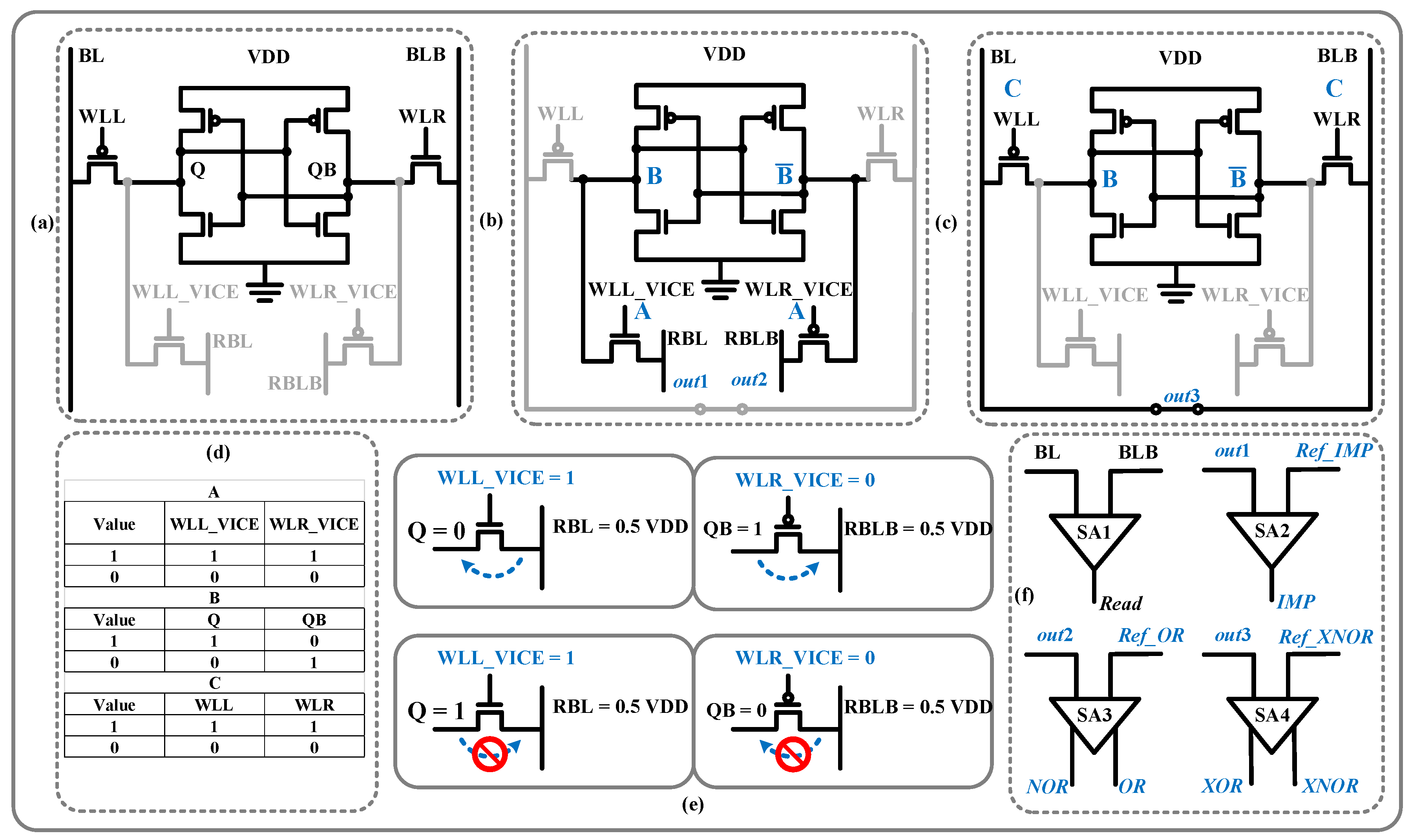

Multifunctional computing-in-memory SRAM cells based on two-surface-channel MoS2 transistors - ScienceDirect

Concept of SRAM with majority logic. (a) Schematic, and (b) flag bit.... | Download Scientific Diagram

![PDF] A 28-nm Compute SRAM With Bit-Serial Logic/Arithmetic Operations for Programmable In-Memory Vector Computing | Semantic Scholar PDF] A 28-nm Compute SRAM With Bit-Serial Logic/Arithmetic Operations for Programmable In-Memory Vector Computing | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/4492954219035e0111652e49d71aa2eff9cea775/3-Figure2-1.png)

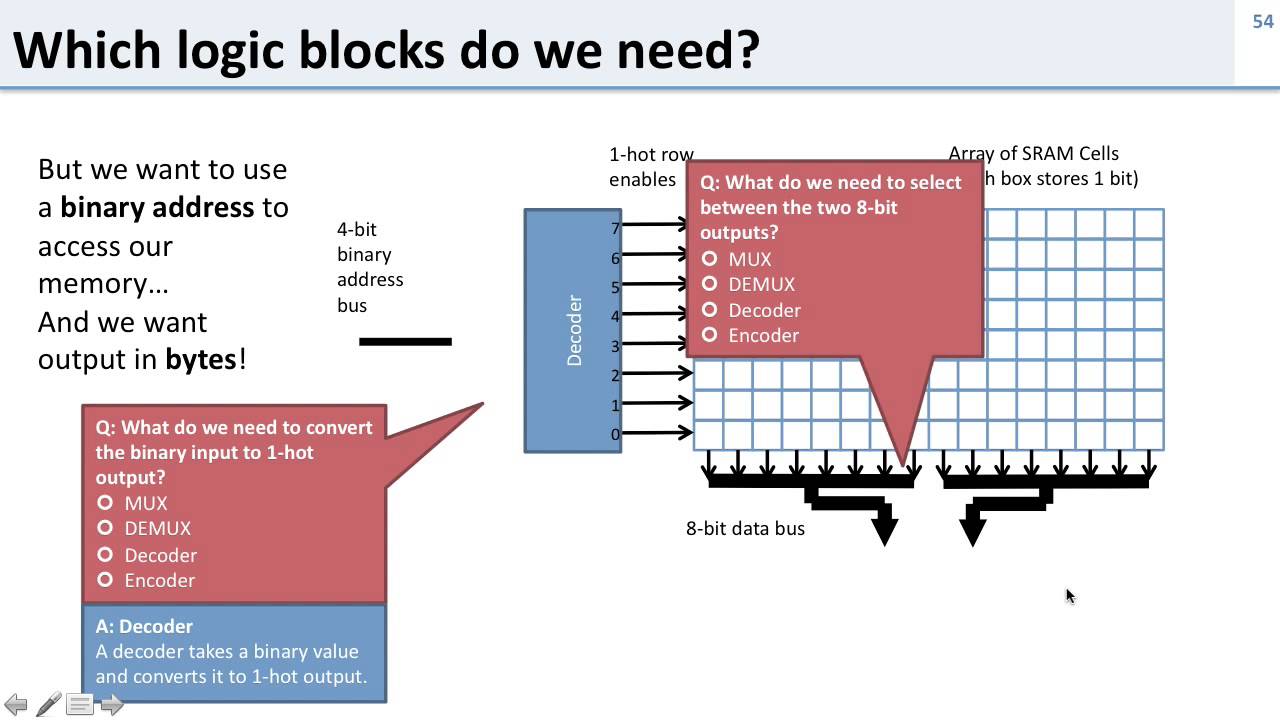

PDF] A 28-nm Compute SRAM With Bit-Serial Logic/Arithmetic Operations for Programmable In-Memory Vector Computing | Semantic Scholar

A Memory-Based Logic Block With Optimized-for-Read SRAM for Energy-Efficient Reconfigurable Computing Fabric | Semantic Scholar

![Schematic of read and write circuits of the SRAM cell [6] and the... | Download Scientific Diagram Schematic of read and write circuits of the SRAM cell [6] and the... | Download Scientific Diagram](https://www.researchgate.net/profile/Govind-Prasad-6/publication/269577949/figure/fig4/AS:1034855328542721@1623740145218/Schematic-of-read-and-write-circuits-of-the-SRAM-cell-6-and-the-additional-logic-for.png)

![PDF] Design and Analysis of 8 T / 10 T SRAM cell using Charge Recycling Logic | Semantic Scholar PDF] Design and Analysis of 8 T / 10 T SRAM cell using Charge Recycling Logic | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/4201c01382e233cfb90a2b45050c93cba1c81201/3-Figure2-1.png)